# Study on the Manufacturability of X Dimension Fan Out Integration Package with Organic RDLs (XDFOI-O)

Haijie Chen\*, Ziyao Bian, Tao Liu, Jielei Xie, Jingyu Wu, Yaojian Lin, and Choon Heung Lee

Abstract—The concept of chiplet was proposed in the post-Moore era. How to layout the multiple chips with different processes and sizes in the package structure is a problem that needs to be considered as different layouts may significantly affect the manufacturability during the packaging process. XDFOI-O is a 2.5D organic interposer structure with a significant coefficient of thermal expansion mismatch in it. Different layouts may cause excessive stress concentration in the package structure, as well as large wafer warpage, which can affect the normal operations of the production line. Stress accumulation on specific chiplet during the wafer thinning process is another manufacturability problem, leading to chip cracking. Prospective finite element analysis can be applied to evaluate the various layouts. In simulation work, different placement processes of dummy chips as stiffeners, as well as different chiplet thicknesses and underfill coverage, can be used as factors for simulation studies, thereby making a reference for further chiplet package design.

*Keywords*—Chiplet, manufacturability, RDL interposer, wafer thinning, XDFOI-O

# Introduction

With the increasing cost of advanced wafer manufacturing processes in a foundry, the concept of chiplet has gained increasing attention in the post-Moore era [1-2]. Chiplet is the concept of breaking down the functions of a single system on chip into numerous small chips and then using advanced packaging technology (MCM/2.5D/3-D, etc.) to reassemble a large and complex system into one package, thereby reducing the total cost of the chip. Some modules do not require the use of the most advanced wafer process, and can also utilize some chiplets in subsequent projects to achieve IP reuse and significantly reduce the costs [3-5].

The implementation methods of chiplet packaging mainly include the following: MCM, 2.5D packaging, and 3-D packaging. At present, 2.5D packaging is the mainstream method of chiplet packaging, which refers to the packaging of high-density I/O interconnections between chiplets through interposer layers, characterized by the ability to integrate multiple dice and achieve high density. According to the current technologies, 2.5D packaging is mainly divided into redistribution layer (RDL) interposer and Si interposer. RDL interposer packaging enables multiple chips to be electrically connected at the

The manuscript was received on November 13, 2023; revision received on January 14, 2024; accepted on January 24, 2024.

JCET Group Co., Ltd., No.78 Changshan Road, Jiangyin, Jiangsu, People's Republic of China

\*Corresponding author; email: hugh.chen@jcetglobal.com

wafer level through RDLs. Compared with traditional MCM packaging, RDL interposer packaging technology can reduce the distance between chips, significantly reducing the signal connection width and spacing. In addition, compared with the Si integrator, the 2.5D RDL interposer eliminates the silicon through via (TSV) process, has lower thermal resistance and better mechanical properties [5-6], and has significant cost advantages. Therefore, the 2.5D RDL interposer (named XDFOI-O, X dimension fan out integration [7] with organic RDLs, in this paper) is a more balanced chip solution in all aspects. At present, the minimum line width/spacing of the RDL interposer can be 2 μm/2 μm and the layer counts reach 6 to form a 6P6M (6 passivation layers and 6 metal layers) routing structure. The distance between chips can reach 60–100 µm. The dielectric layer is made of polymer material, with a thermal expansion coefficient similar to that of the substrate, which can reduce the mechanical stress on chiplet. In addition, due to the bumping process used in the middle-end packaging, which has a role of outsourced semiconductor assembly and testing (OSAT), the size of the metal copper in the RDL interposer can be made larger in tandem with a lower resistivity, which can significantly reduce the signal transmission loss through RDLs [7].

XDFOI-O has already been elaborated on in previous work [8], while only the consistent thickness of each chiplet was considered, and the possible impact of silicon stiffener structure was not taken into account. Therefore, there was a lack of assessment of the impact of stress and warpage differences on manufacturability. There are numerous studies [9-11] on the impact of the wafer thinning process on specific package structure. Similar process steps in XDFOI-O are highly likely to have a significant impact on the structure and final yield of the package. All these influence factors need to be considered together.

In this work, XDFOI-O packaging was mainly explored in two aspects. Firstly, under the constraint that the packaging area is defined specifically, chiplets cannot fully fill the entire packaging area and the stress issue may happen in the following processes. Finite element analysis (FEA) simulation was conducted on the layout and the structure of stiffeners, thus providing some directional guidance for layout. Secondly, due to the fact that chiplets may come from different suppliers and have significant differences in the size and thickness of their incoming materials, subsequent processes may also face challenges after assembly onto interposer wafers Therefore, we discussed the subsequent processes and provided directional guidance for incoming materials. Through this investigation, it is expected to improve efficiency and accelerate the introduction of chiplet products in terms of manufacturability.

### EXPERIMENTAL METHODS

# A. Test Package Structure

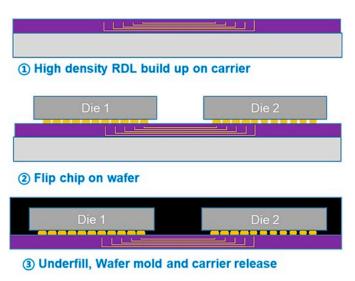

Fig. 1 illustrates the process flow of XDFOI-O. The entire flow is a typical RDL-first process, divided into six major steps. Firstly, high-density RDLs are completed on the carrier wafer for chip interconnection. Then flip the chip onto the high-density RDLs, and encapsulate the chip with underfill and wafer molding materials. Grind the back of the chip and molding compound to expose the silicon, remove the carrier wafer, and perform bumping on the other side to produce C4 (controlled collapse chip connection) bumps. Finally, metals can be selectively deposited on the wafer back to achieve high-performance heat dissipation of the package. The reconstructed package may have a significant impact on the stress of the C4 in Step 5 and the following fcBGA processes [11].

The chiplet sets and the package size are shown in Table I. In this XDFOI-O package, assuming the package functionality

Fig. 1. XDFOI-O process flow.

Table I

The Chiplet Sets, Package Size, and Underfill Coverage in this Evaluation

| Chiplet           |                  | Thickness |     |           |     |  |  |

|-------------------|------------------|-----------|-----|-----------|-----|--|--|

|                   | Size             | A-1       | A-2 | B-1       | B-2 |  |  |

| Chip A            | $16.7 \times 10$ |           | 7:  | 50        |     |  |  |

| Chip B            | $4.8 \times 3.2$ | 750       | 750 | 300       | 300 |  |  |

| Chip C            | $0.6 \times 0.4$ | 300       | 300 | 750       | 750 |  |  |

| Package           | $19 \times 16$   |           | 7:  | 50        |     |  |  |

| Underfill on chip |                  | $\sqrt{}$ | ×   | $\sqrt{}$ | ×   |  |  |

can form a complete system, three chips, namely computing chip (A), memory chip (B), and I/O (input/output) chip (C), are assigned the sizes of 16.7  $\times$  10 mm, 4.8  $\times$  3.2 mm, and 0.6  $\times$ 0.4 mm, respectively. The size of the primary packaging body is 19 × 16 mm. There is obvious area redundancy in distributing the three chips into the packaging body, and optimization of the layout is needed. Stiffeners should be configured in the structure to reduce the stress inside the packaging body and increase the process window and yield for subsequent processes. Table II shows the combinations of three types of chips and stiffeners. From the schematic diagram, it can be seen that the scheme involves a total of three types of chip and stiffener combinations. In Layout 1, D-0 replicates Chip B, with the same size and thickness. Layout 2 adds stiffeners D-1 on Layout 1, and Layout 3 adds stiffeners on the two previous layouts. After D-2 is added, the combination of the right chip and stiffer is flush with Chip A. For ease of comparison, both the chip and stiffener are made of the same silicon material and have the same thickness. In addition, the connection between the stiffeners and the reconstructed wafer is evaluated using two methods, namely die-attach film (DAF) or conventional flip-chip (FC) interconnection; therefore, the assembly processes of

Table II

The Layout of Chiplets and Stiffeners

| Layout options | Schematic                               |  |  |  |  |  |  |

|----------------|-----------------------------------------|--|--|--|--|--|--|

| Layout 1       | D-0 A B B                               |  |  |  |  |  |  |

| Layout 2       | A C D-1 B B B                           |  |  |  |  |  |  |

| Layout 3       | A C D-1 B D-2 D-2 C D-1 C D-1 D-0 C D-1 |  |  |  |  |  |  |

silicon stiffeners are divided into DA (die attachment) and flipchip attachment. For the FC method, after the interconnection, the bottom of the chip is filled with underfill material.

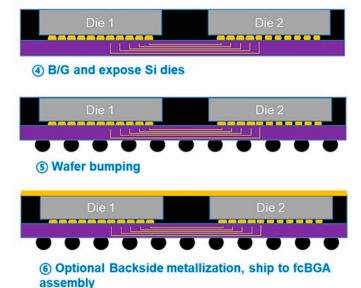

According to the layout shown in Table II, the best combination can be preliminarily obtained after simulation. On this basis, further research will be conducted on the subsequent processes. Although in the layout simulation, it is assumed that both chips and stiffeners have the same thickness, while in actual production, it is difficult for small chips to have the same thickness setting as large chips. Due to the need for thicker chips to maintain the feasibility of FC and other processes, small chips may need to be thinned in advance due to the insufficient sawing street dimension for blade singulation. As shown in Fig. 2 (under a microscope), without controlling the thickness of the incoming chiplets, it is easy to detect chip cracking issues in the distinguishing area after wafer thinning, which seriously affects the yield of the product. Therefore, as a further combination adjustment compared with that in Table III, the thickness of Chip B and Chip C is adjusted, and an extreme assumption is made for underfill coverage, that is, the thinnest chip has underfill coverage on the chip back due to the material properties. Finally, the dynamic simulation is conducted to verify the tendency. The setting conditions are shown in Table III.

### B. Simulation Work Description

For the different package layouts, the FEA software ANSYS with the Statics module is applied to study the characteristics of stress performance. The dielectric layer on chip is not modeled in the FEA, so only stresses on the different materials and the total package deformation are compared.

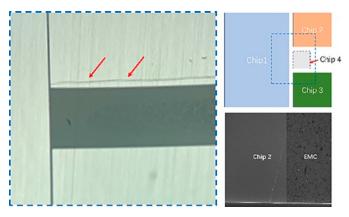

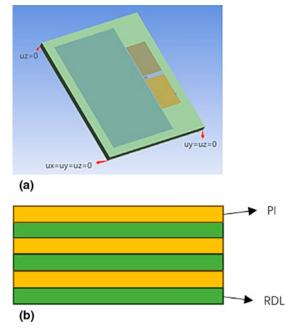

For example, build the model using Layout 1-1 in Table II, as shown in Fig.3. Simplify multilayer RDLs in a stacked form with RDL and PI thicknesses unchanged. Select a reflux temperature of 175°C, at which epoxy molding compound (EMC) molding material is in a liquid or near liquid state that cannot take any stress without stiffness, as the stress-free temperature, and then extract the stress at room temperature. Table III shows the material properties and only linear elasticity is considered for all materials. Try to choose a hexahedral mesh as much as possible. Due to the special nature of solder balls, it is a tetrahedral mesh, as shown in Fig. 4.

Fig. 2. Chip cracking after wafer thinning (Chip 4 is covered by EMC).

Table III

Material Properties of XDFOI-O Package

| Item    |            | Unit   | Si   | Copper | ΡI  | SnAg | EMC | Underfill | DAF   |

|---------|------------|--------|------|--------|-----|------|-----|-----------|-------|

| Tg      |            | °C     | NA   | NA     | 230 | NA   | 160 | 95        | 177   |

| CTE     | $\alpha 1$ | ppm/°C | 2.62 | 17     | 65  | 22.5 | 9   | 25        | 144   |

|         | $\alpha 2$ | ppm/°C |      |        |     |      | 38  | 95        | 188   |

| E       | 25 C       | GPa    | 129  | 110    | 3.5 | 11.6 | 18  | 11        | 0.6   |

|         | 260 C      | GPa    |      |        |     |      | 2.5 | 0.15      | 0.002 |

| Poisson | 's ratio   | -      | 0.28 | 0.33   | 0.3 | 0.4  | 0.3 | 0.3       | 0.3   |

Furthermore, ANSYS/LS-DYNA is applied to develop a dynamic finite element modeling method for the wafer thinning process. To simulate the effect of wafer thinning on the stress around the chip, a dynamic modeling method for the influence of underfill thickness was established. Boundary conditions are defined in the three-dimensional strain model. The bottom of the wafer is fixed, and the upper surface is free. Model the grinding wheel as a rigid body. The grinder comes into contact with the wafer at a fixed speed. Defined the frictional contact between the grinding machine and the wafer surface. Simulated the friction effect between the grinding machine and the wafer surface, When a high-speed grinding machine impacts the wafer surface, this impact load introduces dynamic stress into the wafer.

Taking the previous Table I's solution as an example, Chip A has a larger size and is set to the normal original chip thickness. However, Chips B and C may require pre-thinning due to their small size in order to perform better singulation. In actual operations, Chips B and C may have different thicknesses (less than half the thickness of the other two chips), and chips are covered with underfill creeping on the back of the chip (set the thickness of underfill 25  $\mu$ m). Table III is the combination of chip thickness and underfill coverage.

Fig. 3. Model simplification (a) Top view, (b) Multilayer RDL equivalent.

Fig. 4. Model mesh generation.

### RESULTS AND DISCUSSION

# A. Stress Analysis Between the Layouts

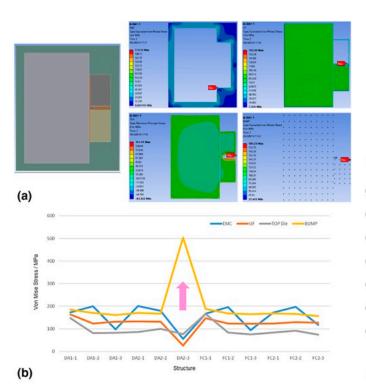

Considering the situation in Fig. 2, where there is cracking during the packaging process, it is necessary to pay close attention to the stress situation during chip layout. Generally, as the material gradually accumulates, the mismatch of CTE will cause stress generation. For this known possible anomaly, it is necessary to analyze the stress distribution of adjacent materials. Simulate the corresponding stress of the structure in Table II and summarize the stress of each layer. As the crack situation occurs on chip silicon, the chip, underfill, molding compound, and the adjacent chip bumps are analyzed with emphasis. Fig. 5a analyzes the stress in each layer through a peeling-off analysis of Structure DA1-1 as an example, and displays all the structure results in Fig. 5b. It can be seen that except for the structure of DA2-3, the stress difference between each layer is not significant under the same chip layout, which

Fig. 5. Stress distribution by layer of different XDFOI-O layouts.

means that whether it is a die-attach or FC method, the impact on stress tends to be consistent. DA2-3 has less stress in the top die, underfill, and molding compound layers except the bump layer, it can be explained that with the introduction of more polymer materials, more stress is concentrated on the bumps of the live chip, resulting in a stress blockage in stress transmission.

### B. Warpage Analysis Between the Layouts

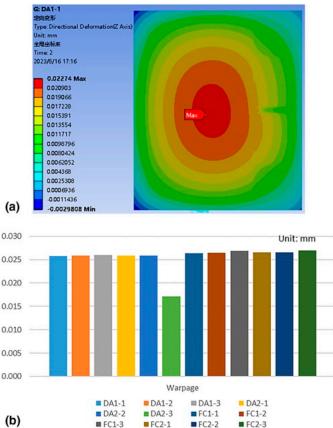

The warpage data of different XDFOI-O packaging structures can be obtained from Fig. 6, where Fig. 6a is a typical schematic diagram of warpage simulation for DA1-1, and Fig. 6b is a summary of specific layout warpage data. From this figure, the overall warpage difference of the packages is not significant in most cases, locating between 25 and 30  $\mu m$ . However, there is a significant change in the warpage of the DA2-3 structure, with a decrease of approximately 30%. The explanation for this result can be attributed to the fact that the size of Chip B is significantly larger than that of Chip C, and its support capacity is stronger. Positioning Chip B in the middle of the right side of the package can significantly increase the stiffness of the package, and with the addition of D-2, it can reduce the warpage. In addition, DA2-3 does not have a similar effect, possibly due to the larger CTE of DAF. Underfill material combined with micropillar bumps and silicon has a greater effect on the CTE mismatch with the RDL interposer, resulting in a reduced ability to mitigate the warpage.

Fig. 6. Warpage distribution of different XDFOI-O layouts.

Fig. 7. Effect analysis of chip thickness in XDFOI-O layouts.

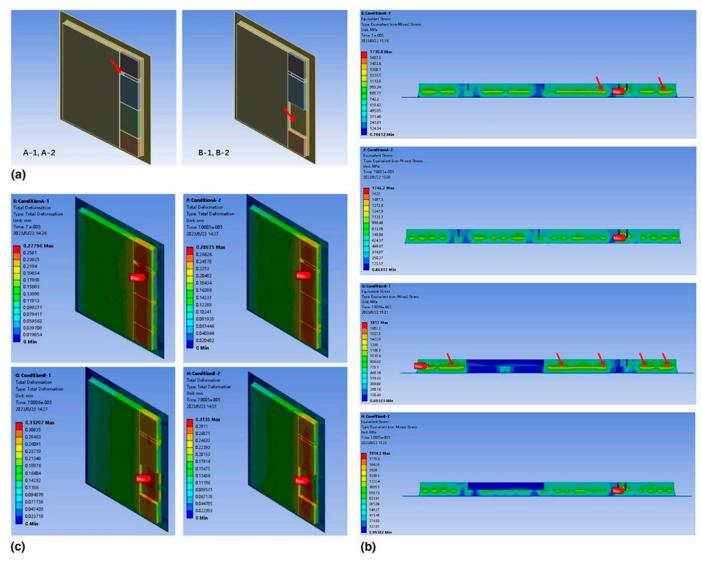

# C. Effect Analysis of Chip Thickness

Furthermore, based on the cracking phenomenon observed in the XDFOI-O structure during the process, a corresponding dynamic analysis was conducted as in Fig. 7a. Equivalent stress and total deformation results are shown in Figs. 7b and 7c. In fact, in the actual thinning process, the grinding wheel and wafer rotate in opposite directions at a certain speed and angle. For the sake of model simplification, this simulation focuses more on the cause of chip cracking, and this condition has not been further set. Assuming that the grinding wheel presses toward the wafer at a certain speed and pressure, observe the changes in internal stress in the model during this process. From the results, it can be seen that with the application of grinding extrusion stress, normally the maximum stress concentration is distributed around the thin chip, which is consistent with the situation where chip cracking occurs at the thin chip during the process. When there is underfill creeping on the back of the thin chip, more severe stress and deformation spread around the thin chip as indicated in Figs. 7b and 7c.

From the material properties in Table III, the elastic modulus of EMC or underfill is significantly lower than that of silicon materials, while for the encapsulation materials, EMC also has a much higher elastic modulus than underfill. In these cases, thin chips are encapsulated by more underfill materials, resulting in a significant increase in deformation and weakened support in this area during the thinning process. More stress will be added to surrounding silicon materials, leading to cracking of the chips located in this area.

# CONCLUSION

This paper selects a chip size and thickness combination for XDFOI-O packaging, conducts stress and warpage analysis on different layouts, and simulates the subsequent wafer thinning process. Different chip bonding methods, except for the full use of die attachment, have similar warpage conditions. However, during stress analysis, it is found that EMC, UF, and top die are subjected to relatively small stresses, with a large

amount of stress concentrated in bumps. This creates some obstacles for the selection of this solution. Therefore, in actual production, more consideration should be given to the convenience of manufacturing, such as increasing manufacturing efficiency through repeated use of the same type of equipment, and stiffener chip sizes that are more convenient to pick and place. During dynamic analysis, it is also found that significant stress is found crowding around the thinner chip due to the smaller modulus of the polymer materials.

Therefore, during the introduction phase of the XDFOI-O product, the use of FEA can achieve the stress and warping analysis, then support the design of layouts based on conditions, and thereby improve product design quality. Through the results of FEA, targeted optimization of wafer thinning process parameters can be conducted to minimize the yield loss in production and finally improve product manufacturability.

# ACKNOWLEDGMENTS

The author would like to thank the JCET XDFOI team for the modeling, wafer tape-out, and assembly work, and thank JCET Design Service BU for the XDFOI-O design instructions.

### REFERENCES

- J.H. Lau, "Recent advances and trends in multiple system and heterogeneous integration with TSV-less interposers," *IEEE Transactions on Components*, Packaging and Manufacturing Technology, Vol. 12, pp. 1271-1281, 2022.

- [2] N. Motohashi, T. Kimura, K. Mineo, Y. Yamada, T. Nishiyama, K. Shibuya, H. Kobayashi, Y. Krita, and M. Kawano, "System in a wafer-level package technology with RDL-first process," IEEE 61st Electronic

- Components and Technology Conference (ECTC), pp. 59-64, Lake Buena Vista, FL, 31 May 2011 03 June 2011.

- [3] M. Lin, M. Liu, H. Chen, S. Chen, M. Yew, C. Chen, and S. Jeng, "Organic interposer CoWoS-R (plus) technology," IEEE 72nd Electronic Components and Technology Conference (ECTC), pp. 1-6, San Diego, CA, 31 May 2022 - 03 June 2022.

- [4] T. Lee, S. Yang, H. Wu, and Y. Lin, "Chip last fanout chip on substrate (FOCoS) solution for chiplets integration," IEEE 72nd Electronic Components and Technology Conference (ECTC), pp. 1970-1974. San Diego, CA, USA, 31 May 2022 - 03 June 2022.

- [5] X. Zhang, Y. Wang, J.-H. Im, and P.S. Ho, "Chip—package interaction and reliability improvement by structure optimization for ultralow-k interconnects in Flip-Chip packages," *IEEE Transactions on Device and Materials Reliability*, Vol. 12, pp. 462-469, 2012.

- [6] Ganesh Hariharan, Raghunandan Chaware, Inderjit Singh, Jeff Lin, Laurene Yip, Kenny Ng, and SY Pai, "A comprehensive reliability study on a CoWoS 3D IC package," IEEE 65th Electronic Components and Technology Conference (ECTC), pp. 573-577, San Diego, CA, USA, 26-29 May 2015.

- [7] Yi-Hang Lin, M.C. Yew, S.M. Chen, M.S. Liu, Pravin Kavle, T.M. Lai, C.T. Yu, F.C. Hsu, C.S. Chen, T.J. Fang, C.K. Hsu, K.C. Lee, C.H. Lin, P.Y. Lin, and Shin-Puu Jeng, "Multilayer RDL interposer for heterogeneous device and module integration," IEEE 69th Electronic Components and Technology Conference (ECTC), pp. 921-936, Las Vegas, NV, USA, 28-31 May 2019.

- [8] H. Chen, Z. Hu, C. Wang, M. He, J. Xie, Y. Lin, and C.H. Lee, "Study on CPI behaviors of X dimension fan-out integration (XDFOI) packages," *IMAPSource Proceedings*, Vol. 2022, pp. 382-388, 2023.

- [9] H.N. Li, T.B. Yu, L.D. Zhu, and W.S. Wang, "Analytical modeling of grinding-induced subsurface damage in monocrystalline silicon," *Materials & Design*, Vol. 130, pp. 250-262, 2017.

- [10] G. Li, C. Xiao, S. Zhang, R. Sun, and Y. Wu, Journal of Materials Processing Technology, Vol. 301, pp. 117453-14, 2022.

- [11] F.X. Che, "Dynamic stress modeling on wafer thinning process and reliability analysis for TSV wafer," *IEEE Transactions on Components, Pack*aging and Manufacturing Technology, Vol. 4, pp. 1432-1440, 2014.