# Critical Issues of TSV and 3D IC Integration

John H. Lau

Abstract—Moore's law has been the most powerful driver for the development of the microelectronic industry. This law is grounded in lithography scaling and integration (in 2D) of all functions on a single chip, perhaps through system-on-chip (SoC). On the other hand, the integration of all these functions can be achieved through system-in-package (SiP) or, ultimately, 3D IC integration. However, there are many critical issues for 3D IC integration. In this study, some of the critical issues will be discussed and some potential solutions or research problems will be proposed.

Keywords—3D IC integration, TSV with RDL, solder microbumps, MEOL, thin wafer handling, thermal management

### Introduction

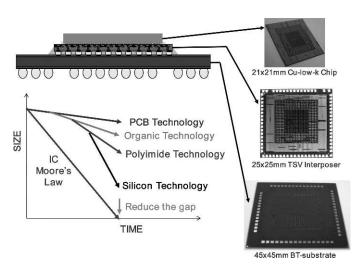

The invention of the transistor by Bardeen, Brattain, and Shockley of Bell Laboratory in 1947 (which earned them the 1956 Nobel Prize) foreshadowed the development of generations of computers and smart phones. The invention of the silicon integrated circuit (IC) by Jack Kilby of Texas Instruments in 1958 and 6 mo later by Robert Noyce of Fairchild Semiconductor excited the development of generations of integrations. The proposal (for minimum cost) of doubling the number of transistors on an IC every 24 mo by Gordon Moore in 1965 (also called Moore's law) has been the most powerful driver for the development of the microelectronic industry in the past 44 y. This law arose from the field of lithography scaling and integration (in 2D) of all functions on a single chip, and has been true through the system-on-chip (SoC) advances.

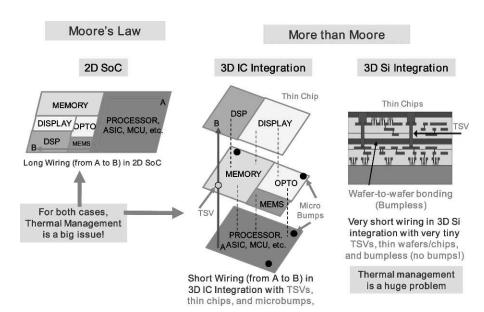

Taking it to the next level, integration of all these functions can be achieved through system-in-package (SiP) or, ultimately, 3D IC integration, which is one of the "more-than-Moore" applications. (Based on the silicon platform technology, anything that involves the integration of electronics, photonics, mechanics, chemistry, heat, magnetics, biology, etc., for functionality and system performance when interacting with people and the environment, is known as more-than-Moore.)

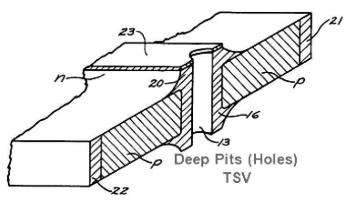

TSV is the heart of 3D integration technology. Fig. 1 shows the patent "Semiconductive Wafer and Method of Making the Same" filed on October 23, 1958 and granted on July 17, 1962 by William Shockley. Yes, the same William Shockley, who coinvented the greatest invention of all time in Electronics Industry—the transistor. Please see "Who invented TSV and When?" posted at 3D InCites on April 24, 2010 (http://www.semineedle.com/posting/31171).

Manuscript received November 2009 and accepted May 2010

Electronics & Optoelectronics Laboratory (EOL), Industrial Technology

Research Institute (ITRI), Chutung, Hsinchu, Taiwan 310, Republic of China

email: johnlau@itri.org.tw

It should be pointed out that besides TSV there is another group of much smaller vias (<0.1 µm in diameter) on a chip as shown in Fig. 2. These tiny vias are connected to devices such as transistors (four tiny vias for each transistor) to build the first metal layer. Today, the number of these tiny vias, for many chips, already exceeds the world population of over 7 billion. These vias, which the semiconductor foundries can do best, are one of their core competences and major businesses. On the other hand, for the "huge" vias that we called TSV for 3D IC integration, the number is many times fewer and the size is many times larger. These TSV are done best by packaging assembly and test houses. Also, they build 3D IC integration packages for the TSV chips and to perform the final tests. Then, they ship only the good ones to EMS (electronics manufacturing services) who perform the PCB assembly, in-circuit test, final assembly, system (also called final or functional) test, and ship the product to the system houses' hubs for distribution. Some system houses prefer to have their EMS ship them the in-circuit tested good PCBs, perform the final test in-house, and then ship the product. This is the infrastructure and how the electronics industry works. Of course, for some special reasons or niche applications, there are always a few exceptions.

3D IC integration is the key technology for electronic products which must meet the following requirements:

- (1) Form factor, smaller is better. For example, PDAs, cameras, cell phones (COMS image sensors).

- (2) Performance, faster is better. For example, shorten local and global interconnect lengths.

- (3) Cost, cheaper is better. For example, system improvements without the high cost of scaling.

- (4) Reliability, low-risk is better. For example, it still works after drops.

The Holy Grail of 3D IC integration (e.g., heterogeneous integration) is shown in Fig. 3, where all the chips, for example, microdisplay, MEMS, memory, microprocessor, optoelectronic, multiple output dc-dc converter, digital signal processor, microbattery, and analog-to-digital (A/D) mixed signal are combined and stacked in three dimensions. It can be seen that, in general, the electrical performance of 3D IC integration is better than that of 2D SoC. However there are many critical issues in questing for the Holy Grail. Some of the critical issues will be discussed and some potential solutions or research problems will be proposed in this study.

## **3D INTEGRATION**

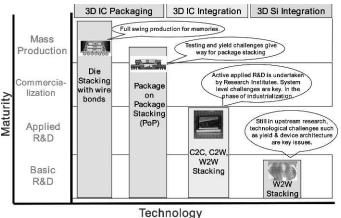

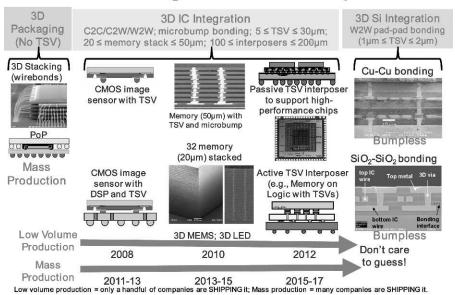

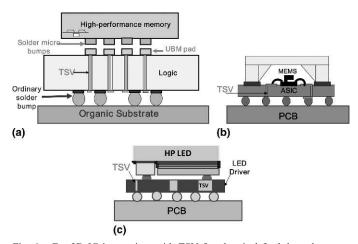

Fig. 4 shows three different groups of 3D integrations, namely: (1) 3D IC packaging, (2) 3D IC integration, and

Fig. 1. TSV invented by Shockley (US Patent # 3,3044,909, filed on October 23, 1958 and granted on July 17, 1962).

Fig. 2. Tiny vias (not the TSV for 3D IC integration) in a chip. (65  $\mu$ m Cu/low-k by *GlobalFoundries*, 2006.) Today, the number of these tiny vias, for many chips, already exceeds the world's population of over 7 billion.

(3) 3-D Si integration. It can be seen that 3D IC packaging is a mature technology and in mass production; thus it will not be discussed herein. The biggest difference between 3D IC packaging and 3D IC/Si integrations is that the integrations two use TSV and 3D IC packaging does not. The biggest difference between 3D IC integration [1-41] and 3D Si integration [42-61] is that 3D Si integration is assembled only by the method of wafer-to-wafer bonding and is bumpless. A 3D integration roadmap is shown in Fig. 5. Since there is no volume production in sight of the 3D Si integration in the next 10 years, it will not be discussed herein.

### A. FEOL, BEOL, and MEOL

FEOL (front end of line) is usually performed in wafer fabs (to pattern the active devices, e.g., transistors, resistors, etc.) and the process is from a bare wafer to passivation, which covers everything except the bonding pads for the next level of interconnect. BEOL (back end of line) is usually performed

Fig. 4. Status of 3D integration technologies.

Fig. 3. Moore's law (2D SoC) versus more-than-Moore (3D IC/Si integrations).

# 3D Integration Roadmap

Fig. 5. 3D integration roadmap.

in packaging assembly and test houses and it involves everything after passivation, for example, UBM (under bump metallurgy), wirebonding, metallization, wafer bumping, backgrinding, and dicing. MEOL (mid end of line) is usually performed by integrating the FEOL and BEOL technologies into a 3D IC integration technology which involves, for example, TSV, microbumps, thin-wafer handling, metallization, UBM, wafer bumping, backgrinding, and dicing. (Please note that semiconductor people have a slightly different definition of FEOL and BEOL.)

# B. Critical Issues of 3D IC Integration

Just as with many other new technologies, 3D IC integration still faces many critical issues. In the development of 3D IC integration, the following must be noted and understood [1-41].

- (1) Known good dice (KGDs) are required.

- (2) Design guidelines and software are not available.

- (3) Test methods and equipment are lacking.

- (4) TSV with redistribution layers (RDL) usually are required.

- (5) Microbumps usually are required.

- (6) Wafer thinning and thin-wafer handling during processing are necessary.

- (7) High equipment accuracy is necessary for alignments.

- (8) Fast chips mix with slow chips.

- (9) Large chips mix with small chips.

- (10) 3D IC stacking inspection methodology is needed.

- (11) 3D IC stacking expertise is lacking.

- (12) 3D IC stacking infrastructure is lacking.

- (13) 3D IC stacking standards are lacking.

- (14) Thermal issues: the heat flux generated by stacked multifunctional chips in miniature packages is extremely high.

- (15) Thermal issues: 3D circuits increase total power generated per unit surface area.

- (16) Thermal issues: chips in the 3D stack may be overheated if proper and adequate cooling is not provided.

- (17) Thermal issues: the space between the 3D stack may be too small for cooling channels (i.e., no gap for fluid flow).

- (18) Thermal issues: thin chips may create extreme conditions for on-chip hot spots.

It can be seen that key enabling technologies for 3D IC integration are, among others: (1) TSV with and without RDL, (2) thin-wafer strengthening and handling, (3) microbumping and assembly, and (4) thermal management, which will be briefly discussed herein. Please note that design, test, reliability, and cost are always important, but they are beyond the scope of this study.

## C. TSV with and without RDL

The most important key enabling technology for 3D IC integration is TSV with and without RDL. They provide advanced vertical interconnects and SiP solutions such as C2C, C2W, and W2W stacking; wafer-level packaging and redistribution; interposer packaging; and the shortest electrical path (vertical electrical feed through) between two sides of a silicon chip or interposer. With the TSV, every chip can have two surfaces with circuits allowing for 3D vertical integration as shown in Fig. 6. Just as with many other new technologies, TSVs still face many critical issues. In the development of TSVs, the following must be noted and understood [1-41].

- TSV cost is higher than that of wire bonding, at least for now.

- (2) The only TSV volume product is CMOS image sensors.

- (3) Developments on memory devices are just in the talking stages.

- (4) High-speed logic and processors will come even later.

- (5) TSV design software is lacking.

- (6) TSV design guidelines are not commonly available.

- (7) Copper filling helps on thermal problems but increases TCE (thermal coefficient of expansion).

- (8) Void-free copper filling usually takes a long time (low throughputs).

- (9) The TSV cost for poor-yield IC wafers is high because many TSVs are wasted on the bad dices.

- (10) TSV wafer yields are high (>99.99%).

- (11) There is a high cost for low TSV wafer manufacturing yield, especially for high-cost dices.

- (12) Single-point touch-up on the TSV wafer is difficult.

Fig. 6. For 3D IC integration, with TSV for electrical feed-through, every chip can have two surfaces with circuits. (a) A high-performance memory is supported by a logic (active TSV interposer). (b) A MEMS device is supported by an ASIC with TSV. (c) A high-power LED is supported by an LED driver with TSV.

- (13) TSV wafer warpage is a problem owing to the TCE mismatch between the silicon and copper.

- (14) Thin TSV wafer handling is necessary during all the processes.

- (15) TSV with high aspect ratios are difficult to manufacture at high yield.

- (16) Test methodology and software for TSV are lacking.

- (17) High-volume production tools are lacking and/or expensive.

- (18) TSV inspection methodology and software are lacking.

- (19) TSV expertise, infrastructure, and standards are lacking.

- (20) It is not known which are the cost-effective and reliable TSVs and for specific IC devices.

- (21) It is not known how large the TSV market is.

- (22) The life cycle of TSV is not known.

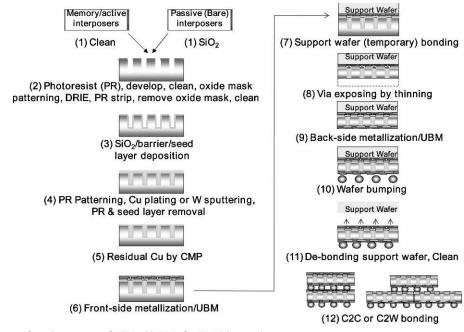

There are many ways to make the TSV for 3D IC integration, for example, via first, via last, via middle, and so on. The most likely manufacturing process used by the industry for making the TSV 3D IC integration is shown in Fig. 7. There are five key steps to making the TSV.

- Via formation by either deep reactive ion etch (DRIE) or laser drilling.

- (2) SiO<sub>2</sub> deposition by either thermal oxidation for passive interposers or PECVD (plasma enhanced chemical vapor deposition).

- (3) Barrier and seed layers deposition by physical vapor deposition (PVD) or electrografting (eG).

- (4) Cu plating or W (tungsten) sputtering to fill the vias.

- (5) CMP (chemical and mechanical polishing) of Cu plating residues (overburden).

It should be noted that for bare wafers such as those for passive interposers, a layer of SiO<sub>2</sub> is needed before the photoresist. For active memory and logic chips and active

Fig. 7. The most likely manufacturing process of TSV with RDL for 3D IC integration.

interposers (e.g., ASIC and processor) because of their passivation layer, only cleaning is needed. The front-side metallization/UBM can be made next on the blind TSV wafer.

In most of the 3D IC integration applications, the thickness of the passive/active interposers ranges from 100  $\mu$ m to 200  $\mu$ m and the stacking memory chips range from 20  $\mu$ m to 50  $\mu$ m. Thus, a support wafer is needed for the remaining processes.

As soon as the support wafer is temporarily bonded to the blind TSV wafer, it can be thinned down to expose the TSV. This step is followed by back-side metallization/UBM and wafer bumping. After that, the support wafer is debonded from the TSV wafer. Finally, the TSV wafer is ready for either W2W bonding (only recommend for high yield IC wafers) or diced into individual chips for C2C or C2W bonding.

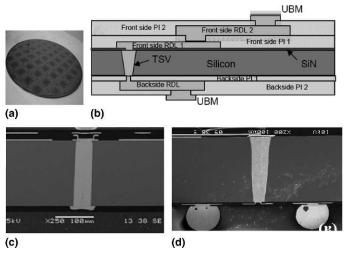

Fig. 8 shows a high performance chip (which cannot be supported by the BT-substrate), and the chip is supported by a passive TSV interposer with two redistribution layers on top and one redistribution layer at the bottom [18]. A simple BT substrate is used to fan out all the I/Os, powers, and grounds to the PCB. Fig. 9 shows the TSV with RDL wafer and the chip with its cross section clearly showing the two RDLs on the top side and one RDL at the bottom side of the interposer [18].

The TSV size should be as small as possible ( $\leq$ 30 µm). The reasons for this are because: (1) there is less thermal expansion mismatch between the Si and Cu, (2) there is less Cu plating, (3) there is higher throughput, and (4) there is more space for routing. Vias of 5-10 µm are not uncommon for 3D IC integration. It should be pointed out that for 3D Si integration the via size could be  $\leq$ 1 µm.

# THIN WAFER HANDLING

In order to have low-profile products with 3D IC integration technology, the thickness of the chips/wafers is usually very thin. Making the wafer thin is not a big problem. Most of the backgrinding machines (e.g., Disco) can do the job and grind the wafers to as thin as 5  $\mu m$ . However, handling thin wafers through all the semiconductor fabrication and packaging assembly processes is difficult. Usually, the thin-device wafer is temporarily bonded on a support wafer. Then it goes through all the semicon-

Fig. 8. A high-performance chip supported by a passive TSV interposer soldered on a BT substrate.

ductor fabrication processes, such as metallization, passivation, UBM, and the packaging processes, such as backgrinding and solder bumping. After all these are done, removing the thin wafer from the support wafer poses another big challenge. This study discusses a few methods for handling thin wafers.

The new 3M+SUSS wafer support system [62] enables conventional backgrinding equipment to be used to produce wafers with a final thickness as low as 20 µm. The key to the system is its ability to provide a rigid, uniform support surface to minimize stress on the wafer as the silicon is removed, resulting in less cracking and chipping. The system includes both the equipment and consumables [3M UV-Curable Liquid Adhesive LC-2201, glass support plate (typically recycled, can be reused many times), and 3M light-to-heat Conversion Solution] necessary for mounting, demounting, and removing adhesive from the wafer.

In the 3M+SUSS system, a glass plate is used to support the wafer through the backgrinding process. A UV-curable liquid adhesive is used as the bonding agent between the device wafer and the glass plate (support wafer). After the backgrinding process, the thinned device wafer is transferred onto a dicing tape, and the support glass is removed by laser debonding of the adhesive-glass interface using a light-to-heat conversion (LTHC) layer. The adhesive can then be removed from the wafer, leaving behind less residue than typically seen with backgrinding tapes. This system also works for other semiconductor and packaging processes as long as the thermal expansion mismatch between the device wafer and the glass plate is within the allowable tolerance.

EVG+Brewer Science have developed a solution that enables temporary bonding of a device wafer to a right carrier substrate (support wafer) and allows not only thinning but also a full range of subsequent processes, including high-temperature deposition, etching, lithography, dielectric application, and curing, plating, and chemical cleaning [63].

# A. Temporary Bonding

The front side of the device wafer and the support wafer are coated with the WaferBOND, an HT Brewer Science adhesive

Fig. 9. TSV wafer (with two RDL on top and one RDL on the bottom) made by the process shown in Fig. 7.

material, by using a coating chamber that includes spin and spray coat capability. Both wafers then are transferred to a bond chamber, where they are carefully centered and vacuum bonded at elevated temperatures. Once the device wafer is temporarily bonded to the support wafer, it is ready for backside processing, including backgrinding, etching, metallization, TSV formation, and so on.

# B. Debonding

During the debonding process, the thin wafer is debonded first via a thermally activated slide liftoff approach from the support wafer, cleaned in a single-wafer cleaning chamber to remove the remaining adhesive residues, and then transferred to the appropriate output format, such as a film-frame carrier, a dedicated wafer cassette, or a coin-stack packing canister. The support wafer is also cleaned and can then be reused immediately for another debonding process.

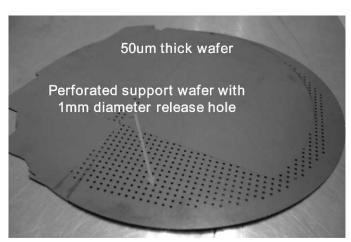

A simple support wafer method for thin wafer (50 µm) handling is shown in Fig. 10 [27]. One of the key problems encountered in the support-wafer method is wafer debonding. The 50-um-thick device wafer is easily broken during the wafer debonding process. This key problem is resolved by optimizing the wafer debonding process to minimize residual stress. The first step is to reduce the pitch of the release hole on the perforated support wafer from 3.5 mm to 2 mm. The second step is to increase the number of perforations on the edge of the support wafer. These two optimized debonding methods allow more chemical solution to uniformly penetrate into the bonding adhesive and eventually debond the wafers successfully. For example, the thin (50  $\mu$ m) device wafer is attached to a support wafer and is handled and put in the PECVD chamber for SiO<sub>2</sub> deposition. No wafer cracking is observed during wafer handling and after silicon oxide deposition. Some engineering and process development are required, though.

# LOW-COST LEAD-FREE SOLDER MICROBUMPS

As mentioned earlier, the thickness of chips for 3D IC integration application is thin and thus the conventional flip chip solder bumps ( $\sim \! 100~\mu m$ ) cannot be used for connecting the thin chips. Instead, tiny bumps in the range of 20-30  $\mu m$  are

Fig. 10. A simple support wafer method for thin wafer handling.

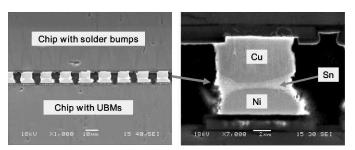

needed. Fig. 11 [10-12] shows the cross sections of the bonding of two Si chips (the bottom one is with TSVs). It can be seen that the lead-free solder is pure Sn, the pitch is 15  $\mu$ m, and the circular pad is only 8  $\mu$ m. Underfill is usually needed between two chips, one of which has Cu-plated TSV because of the thermal expansion mismatch. (The equivalent CTE of a copper-filled TSV silicon chip could be as high as 10  $\times$  10<sup>-6</sup>/°C.) Due to the tiny gap between the chips, smaller filler size underfills (max  $\leq$  3  $\mu$ m and ave  $\leq$  0.5  $\mu$ m) are required.

# THERMAL MANAGEMENT OF 3D IC INTEGRATION

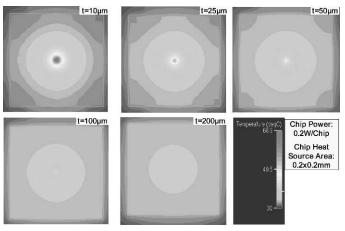

As mentioned earlier, thermal management of 3D IC integration system is important. Two examples are shown in this study. For other results, please see [7]. Fig. 12 shows the temperature maps on a chip for various chip thicknesses. It can be seen that the heat on the chip surface is well dissipated for chip thicknesses of 100-200  $\mu m$  subjected to a generated power of 0.2 W. For the 200- $\mu m$ -thick chip, the temperature distribution is almost uniform and equal to 35°C. However, the hot spot temperature on the chip increases to 69°C (0.2 W power) if the chip thickness is reduced to 10  $\mu m$ , and the hot spot area is clearly shown.

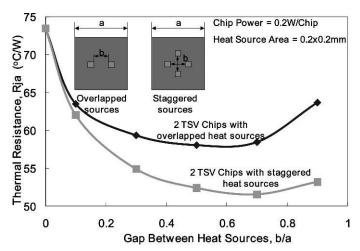

Fig. 13 shows the effect of two heat sources at a distance apart (gap) on the thermal performance of two stacked copper-filled TSV chips. There are two distinct heat sources (each with 0.1 W and on  $0.2 \times 0.2$  mm area) on each chip ( $5 \times 5 \times 0.05$  mm). It can be seen from the left-hand side and upper curve of the figure that (1) the larger the gap ( $b/a \le 0.7$ )

Fig. 11. SEM images of the assembly cross section of an Si chip and Si carrier with lead-free microbumps on 8  $\mu$ m pads and 15  $\mu$ m pitch.

Fig. 12. Temperature maps on a TSV chips with various thickness (hot spot is clearly shown for chip thickness  $< 25 \mu m$ ).

Fig. 13. Thermal resistance of a 3D integration of two Cu-filled TSV chips subjected to two distinct overlapped heat sources and staggered heat sources.

between the two heat sources, the better is the thermal resistance, and (2) when the gap between the two heat sources is larger than 0.7 (i.e., the heat sources are too close to the edge of the chip), the thermal performance is weaker. This is due to suppressible spreading effects near the edges of the chips.

In addition to the case of overlapping heat sources discussed in the preceding paragraph, the orientation effect (staggered heat sources) of two stacked chips, each with two heat sources at a certain distance apart, on the thermal performance of a 3D SiP is presented in the right-hand side and lower curve of Fig. 13. It can be seen that (1) similar to the case of overlapping heat sources, the larger the gap  $(b/a \le 0.7)$ between those two pairs of staggered heat sources, the lower are the maximum junction temperature and thermal resistance, (2) when the gap between the two pairs of staggered heat sources is larger than 0.7 (i.e., the heat sources are too close to the edge of the chip), the thermal performance is weaker, and (3) the maximum thermal resistance of the 3D SiP with two TSV chips subjected to two pairs of staggered heat sources are lower than those with two pairs of overlapping heat sources. This is so because the staggered heat sources avoid the superimposition of heat sources and thus lead to better thermal performance. This result is useful for the design and layout of 3D SiP because it permits relocation of the heat sources and/or rotation of the chip.

### SUMMARY AND RECOMMENDATIONS

Some critical issues (challenges and opportunities) of TSV and 3D IC integration have been discussed and some potential solutions or research problems have also been proposed in this study. Some important results and recommendations are summarized in the following.

- (1) 3D IC integration is the key technology for electronic products which must meet the requirements of form-factor, performance, cost, and reliability.

- (2) TSV, thin wafer handling, microbumping and assembly, and thermal management are the key enabling technologies for 3D IC integration.

- (3) TSV (with the concept that every chip can have two surfaces with circuits) opens the door for many new and useful applications.

- (4) TSV size should be as small as possible ( $\leq 30 \mu m$ ). A size range of 5-10  $\mu m$  for 3D IC integration is not uncommon.

- (5) The thickness of interposers (both passive and active) ranges from 100-200 μm and for the stacking memory chips, the thickness ranges from 20-50 μm.

- (6) The size of low-cost micro bumps connecting the thin chips should be  $\leq$ 25  $\mu m$ .

- (7) The most likely manufacturing process of TSV for most 3D IC integrations is shown in Fig. 7.

- (8) Today, a supporting wafer (carrier) with a special adhesive is necessary for thin wafer handling.

- (9) More developments are needed on low-cost and highquality (such as adhesiveless and carrierless) thin wafer handling methods.

- (10) More research needs to be done on strengthening (such as material improvements and special geometry of) the thin wafers.

- (11) More works need to be done on reliable ultra fine-pitch microbumping and assembly. Underfills with fine filler sizes are needed.

- (12) Cost-effective thermal management methods for 3D IC integration systems are desperately needed.

- (13) Due to very thin chip thickness, special attention should be paid to hot spot temperature.

- (14) The focus of this study is on the technology such as the TSV (the heart) of 3D IC integration. It should be pointed out that the soul of 3D IC integration lies in design and testing.

- (15) The industry should build an ecosystem such as the standards and infrastructures for the 3D IC integration as soon as possible; so the EDA (electronic design automation) vendors would seriously and systematically write the software for the design, simulation, analysis and verification, manufacturing preparation, and testing of 3D IC integration SiP.

### ACKNOWLEDGMENTS

The author would like to thank Dr. Zhang Xiaowu, Dr. Yu Aibin, and Dr. Tang Gong Yue for their useful inputs and constructive help. He also would like to thank Dr. Ian Yi-Jen Chan for his strong support.

# REFERENCES

- [1] J.H. Lau, "Reliability of RoHS Compliant 2D & 3D IC Interconnects," New York, McGraw-Hill, (in press).

- [2] J.H. Lau, C.K. Lee, C.S. Premachandran, and A. Yu, "Advanced MEMS Packaging," New York, McGraw-Hill, 2010.

- [3] J.H. Lau, "Critical issues of 3D IC integrations," in *Proceedings of IMAPS International Symposium on Microelectronics*, San Jose, CA, 2009, pp. 585-592.

- [4] J.H. Lau, "Key enabling technologies for 3D IC integrations," Professional Development Course, IEEE Electronic & Components Technology Conference, San Diego, CA, 2009.

- [5] J.H. Lau, "Design and process of 3D MEMS packaging," in *Proceedings of IMAPS International Symposium on Microelectronics*, San Jose, CA, 2009, pp. 1-9.

- [6] J.H. Lau, R. Lee, M. Yuen, and P. Chan, "3D LED and IC wafer level packaging," Journal of Microelectronics International, Vol. 27, No. 2, pp. 98-105, 2010.

- [7] J.H. Lau and G. Tang, "Thermal management of 3D IC integration with TSV (through silicon via)," in *IEEE Proceedings of Electronic, Compo*nents & Technology Conference, San Diego, CA, 2009, pp. 635-640.

- [8] J.H. Lau, "TSV manufacturing yield and hidden costs for 3D IC integration," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Las Vegas, NV, 2010, pp. 1031-1041.

- [9] J.H. Lau, "State-of-the-art and trends in 3D integration," Chip Scale Review, March/April, pp. 22-28, 2010.

- [10] A. Yu, J.H. Lau, S. Ho, A. Kumar, Y. Wai, D. Yu, M. Jong, V. Kripesh, D. Pinjala, and D. Kwong, "Study of 15-µm-pitch solder microbumps for 3D IC integration," in *IEEE Proceedings of Electronic Components and Technology Conference*, San Diego, CA, May 2009, pp. 6-10.

- [11] A. Yu, J.H. Lau, S. Ho, A. Kumar, H. Yin, J. Ching, V. Kripesh, D. Pinjala, S. Chen, C. Chan, C. Chao, C. Chiu, M. Huang, and C. Chen, "Three dimensional interconnects with high aspect ratio TSVs and fine pitch solder microbumps," in *IEEE Proceedings of Electronic Components and Technology Conference*, San Diego, CA, May 2009, pp. 350-354. Also, accepted for publication in *IEEE Transactions in Advanced Packaging*.

- [12] A. Yu, A. Kumar, S. Ho, H. Yin, J.H. Lau, J. Ching, V. Kripesh, D. Pinjala, S. Chen, C. Chan, C. Chao, C. Chiu, M. Huang, and C. Chen, "Development of fine pitch solder microbumps for 3D chip stacking," in *IEEE EPTC Proceedings*, Singapore, December 2008, pp. 387-392. Also, to be published in *IEEE Transactions in Advanced Packaging*.

- [13] A. Yu, N. Khan, and G. Archit, D. Pinjala, K. Toh, V. Kripesh, S. Yoon, and J.H. Lau, "Fabrication of silicon carriers with TSV electrical interconnections and embedded thermal solutions for high power 3-D package," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 24-28.

- [14] A. Yu, N. Khan, G. Archit, D. Pinjala, K. Toh, V. Kripesh, S. Yoon, and J.H. Lau, "Development of silicon carriers with embedded thermal solutions for high power 3-D package," IEEE Transactions on Components and Packaging Technology, Vol. 32, No. 3, pp. 566-571, 2009.

- [15] G. Tang, O. Navas, D. Pinjala, J.H. Lau, A. Yu, and V. Kripesh, "Integrated liquid cooling systems for 3-D stacked TSV modules," IEEE Transactions on Components and Packaging Technologies, Vol. 33, No. 1, pp. 184-195, 2010.

- [16] K. Chen, C. Premachandran, K. Choi, C. Ong, X. Ling, A. Khairyanto, B. Ratmin, P. Myo, and J.H. Lau, "C2W bonding method for MEMS applications," in *IEEE Proceedings of Electronics Packaging Technol*ogy Conference, 2008, pp. 1283-1287.

- [17] C.S. Premachandran, J.H. Lau, X. Ling, A. Khairyanto, K. Chen, and E. Myo, "A novel, wafer-level stacking method for low-chip yield and non-uniform, chip-size wafers for MEMS and 3D SIP applications," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 314-318.

- [18] X. Zhang, T. Chai, J.H. Lau, C. Selvanayagam, K. Biswas, S. Liu, D. Pinjala, G. Tang, Y. Ong, S. Vempati, E. Wai, H. Li, B. Liao, N. Ranganathan, V. Kripesh, J. Sun, J. Doricko, and C. Vath, "Development of through silicon via (TSV) interposer technology for large die (21 × 21 mm) fine-pitch Cu/low-k FCBGA package," in *IEEE Proceedings of Electronic, Components & Technology Conference*, San Diego, CA, 2009, pp. 305-312. Also accepted for publication in *IEEE Transactions in Advanced Packaging*.

- [19] G. Hoe, G. Tang, P. Damaruganath, C. Chong, J.H. Lau, X. Zhang, and K. Vaidyanathan, "Effect of TSV interposer on the thermal performance of FCBGA package," in *IEEE Proceedings of Electronics Packaging and Technology Conference*, Singapore, 2009, pp. 778-786.

- [20] W.O. Choi, C.S. Premachandran, S. Ong, X. Ling, E. Liao, K. Ahmad, B. Ratmin, K. Chen, P. Thaw, and J.H. Lau, "Development of novel intermetallic joints using thin film indium based solder by low temperature bonding technology for 3D IC stacking," in *IEEE Proceedings of Electronic, Components & Technology Conference*, San Diego, CA, 2009, pp. 333-338.

- [21] S.R. Vempati, S. Nandar, C. Khong, Y. Lim, K. Vaidyanathan, J.H. Lau, B.P. Liew, K.Y. Au, S. Tanary, A. Fenne, R. Erich, and J. Milla, "Development of 3-D silicon die stacked package using flip chip technology with micro bump interconnects," in *IEEE Proceedings of Electronic, Components & Technology Conference*, San Diego, CA, 2009, pp. 980-987. Also accepted for publication in *IEEE Transactions in CPMT*.

- [22] N. Khan, L. Yu, P. Tan, S. Ho, N. Su, H. Wai, K. Vaidyanathan, D. Pinjala, J.H. Lau, and T. Chuan, "3D packaging with through silicon via (TSV) for electrical and fluidic interconnections," in *IEEE Proceedings of Electronic, Components & Technology Conference*, San Diego, CA, 2009, pp. 1153-1158.

- [23] V.N. Sekhar, S. Lu, A. Kumar, T.C. Chai, V. Lee, S. Wang, X. Zhang, C.S. Premchandran, V. Kripesh, and J.H. Lau, "Effect of wafer back grinding on the mechanical behavior of multilayered low-k for 3D-stack packaging applications," in *IEEE Proceedings of Electronic, Compo*nents & Technology Conference, Orlando, FL, 2008, pp. 1517-1524.

- [24] N. Khan, V. Rao, S. Lim, S. Ho, V. Lee, X. Zhang, R. Yang, E. Liao, and T. Ranganathan, T. Chai, V. Kripesh, and J.H. Lau, "Development of 3D silicon module with TSV for wystem in packaging," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 550-555.

- [25] S. Ho, S. Yoon, Q. Zhou, K. Pasad, V. Kripesh, and J.H. Lau, "High RF performance TSV for silicon carrier for high frequency application," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 1956-1952.

- [26] C. Selvanayagam, J.H. Lau, X. Zhang, S. Seah, K. Vaidyanathan, and T. Chai, "Nonlinear thermal stress/strain analysis of copper filled TSV (through silicon via) and their flip-chip microbumps," IEEE Transactions on Advanced Packaging, Vol. 32, No. 4, pp. 720-728, 2009.

- [27] X. Zhang, A. Kumar, Q.X. Zhang, Y.Y. Ong, S.W. Ho, C.H. Khong, V. Kripesh, J.H. Lau, D.-L. Kwong, V. Sundaram, R. Tummula, and M. Geort, "Application of piezoresistive stress sensors in ultra thin device handling and characterization," Journal of Sensors & Actuators: A, Physical, Vol. 156, No. Nov, pp. 2-7, 2009.

- [28] M. Sekiguchi, H. Numata, N. Sato, T. Shirakawa, M. Matsuo, H. Yoshikawa, M. Yanagida, H. Nakayoshi, and K. Takahashi, "Novel low cost integration of through chip interconnection and application to CMOS image sensor," in *IEEE Proceedings of Electronic Components* and Technology Conference, San Diego, CA, 2006, pp. 1367-1374.

- [29] K. Takahashi and M. Sekiguchi, "Through silicon via and 3-D wafer/chip stacking technology," in *IEEE Proceedings of Symposium on VLSI Circuits Digest of Technical Papers*, 2006, pp. 89-92.

- [30] P. Garrou, C. Bower, and P. Ramm, "3D Integration: Technology and Applications," New York, John Wiley, 2009.

- [31] P. Ramm, M. Wolf, A. Klumpp, R. Wieland, B. Wunderle, B. Michel, and H. Reichl, "Through silicon via technology—Processes and reliability for wafer-level 3D system integration," in *Proceedings of the IEEE ECTC*, Orlando, FL, 2008, pp. 847-852.

- [32] P.S. Andry, C.K. Tsang, B.C. Webb, E.J. Sprogis, S.L. Wright, B. Bang, and D.G. Manzer, "Fabrication and characterization of robust through-silicon vias for silicon-carrier applications," IBM Journal of Research and Development, Vol. 52, No. 6, pp. 571-581, 2008.

- [33] J.U. Knickerbocker, P.S. Andry, B. Dang, R.R. Horton, C S. Patel, R.J. Polastre, K. Sakuma, E.S. Sprogis, C.K. Tsang, B.C. Webb, and S.L. Wright "3-D silicon integration," in *IEEE Proceedings of Electronic Components and Technology Conference*, 2008, pp. 538-543.

- [34] K. Kumagai, Y. Yoneda, H. Izumino, H. Shimojo, M. Sunohara, T. Kurihara, "A silicon interposer BGA package with Cu-filled TSV and multi-layer Cu-plating interconnection," in *IEEE Proceedings of Elec*tronic Components and Technology Conference, Orlando, FL, 2008, pp. 571-576.

- [35] M. Sunohara, T. Tokunaga, T. Kurihara, M. Higashi, "Silicon interposer with TSVs (through silicon vias) and fine multilayer wiring," in *IEEE Proceedings of Electronic Components and Technology Conference*, Orlando, FL, 2008, pp. 847-852.

- [36] H.S. Lee, Y-S. Choi, E. Song, K. Choi, T. Cho, S. Kang, "Power delivery network design for 3D SIP integrated over silicon interposer platform," in *IEEE Proceedings of Electronic Components and Technology Confer*ence, Reno, NV, 2007, pp. 1193-1198.

- [37] M. Matsuo, N. Hayasaka, K. Okumura, "Silicon interposer technology for high-density package," In *IEEE Proceedings of Electronic Compo*nents and Technology Conference, Las Vegas, NV, 2000, pp. 1455-1459.

- [38] E. Wong, J. Minz, and S.K. Lim, "Effective thermal via and decoupling capacitor insertion for 3D system-on-package," in *IEEE Proceedings* of Electronic Components and Technology Conference, San Diego, CA, 2006, pp. 1795-1801.

- [39] R. Beica, C. Sharbono, and T. Ritzdorf, "Through silicon via copper electrodeposition for 3D integration," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 577-583.

- [40] M. Wolf, B. Wunderle, N. Jürgensen, G. Engelmann, O. Ehrmann, B. Michel, T. Dretschkow, A. Uhlig, and H. Reichl, "High aspect ratio TSV copper filling with different seed layers," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 563-570.

- [41] D. Henry, F. Jacquet, M. Neyret, X. Baillin, T. Enot, V. Lapras, C. Brunet-Manquat, J. Charbonnier, B. Aventurier, and N. Sillon, "Through silicon vias technology for CMOS image sensors packaging," in *IEEE Proceedings of Electronic, Components & Technology Conference*, Orlando, FL, 2008, pp. 556-562.

- [42] Y. Akasaka, "Three-dimensional IC trends," Proceedings of the IEEE, Vol. 74, No. 12, pp. 1703-1714, 1986.

- [43] Y. Akasaka and T. Nishimura, "Concept and basic technologies for 3-D IC structure," IEEE Proceedings of International Electron Devices Meetings, Vo., Vol. 32, pp. 488-491, 1986.

- [44] K. Chen, S. Lee, P. Andry, C. Tsang, A. Topop, Y. Lin, J. Lu, A. Young, M. Ieong, and W. Haensch, "Structure, design and process control for Cu bonded interconnects in 3D integrated circuits," in *IEEE Proceedings of International Electron Devices Meeting, (IEDM 2006)*, San Francisco, CA, 2006, pp. 367-370.

- [45] F. Liu, R. Yu, A. Young, J. Doyle, X. Wang, L. Shi, K. Chen, X. Li, D. Dipaola, D. Brown, C. Ryan, J. Hagan, K. Wong, M. Lu, X. Gu, N. Klymko, E. Perfecto, A. Merryman, K. Kelly, S. Purushothaman, S. Koester, R. Wisnieff, and W. Haensch, "A 300-wafer-level three-dimensional integration scheme using tungsten through-silicon fia and hybrid Cu-adhesive bonding," in *IEEE Proceedings of IEDM*, 2008, pp. 1-4.

- [46] R. Yu, F. Liu, R. Polastre, K. Chen, X. Liu, L. Shi, E. Perfecto, N. Klymko, M. Chace, T. Shaw, D. Dimilia, E. Kinser, A. Young, S. Purushothaman, S. Koester, and W. Haensch, "Reliability of a 300-mm-compatible 3DI Technology base on hybrid Cu-adhesive wafer bonding," in *Proceedings of Symposium on VLSI Technology Digest* of Technical Papers, 2009, pp. 170-171.

- [47] A. Shigetou, T. Itoh, K. Sawada, and T. Suga, "Bumpless interconnect of 6-um pitch Cu electrodes at room temperature," in *IEEE Proceedings* of *Electronic & Components Technology Conference*, Lake Buena Vista, FL, 2008, pp. 1405-1409.

- [48] A. Shigetou, T. Itoh, M. Matsuo, N. Hayasaka, K. Okumura, and T. Suga, "Bumpless interconnect through ultrafine Cu electrodes by means of surface-activated bonding (SAB) method," IEEE Transactions on Advanced Packaging, Vol. 29, No. 2, p. 218-226, 2006.

- [49] C. Wang and T. Suga, "A novel moire fringe assisted method for nanoprecision alignment in wafer bonding," in *IEEE Proceedings* of Electronic Components & Technology Conference, San Diego, CA, 2009, pp. 872-878.

- [50] C. Wang and T. Suga, "Moire method for nanoprecision wafer-to-wafer alignment: Theory, simulation and application," in *IEEE Proceedings of International Conference on Electronic Packaging Technology & High Density Packaging*, 2009, pp. 219-224.

- [51] E. Higurashi, D. Chino, T. Suga, and R. Sawada, "Au-Au surfaceactivated bonding and its application to optical microsensors with 3-D

- structure," IEEE Journal on Selected Topics in Quantum Electronics, Vol. 15, No. 5, pp. 1500-1505, 2009.

- [52] J. Burns, B. Aull, C. Keast, C. Chen, and C. Chen, C. Keast, J. Knecht, V. Suntharalingam, K. Warner, P. Wyatt, and D. Yost, "A wafer-scale 3-D circuit integration technology," IEEE Transactions on Electron Devices, Vol. 53, No. 10, pp. 2507-2516, 2006.

- [53] C. Chen, K. Warner, D. Yost, J. Knecht, V. Suntharalingam, C. Chen, J. Burns, and C. Keast, "Sealing three-dimensional SOI integrated-circuit technology," in *IEEE Proceedings of International SOI Conference*, 2007, pp. 87-88.

- [54] C. Chen, C. Chen, D. Yost, J. Knecht, P. Wyatt, J. Burns, K. Warner, P. Gouker, P. Healey, B. Wheeler, and C. Keast, "Three-dimensional integration of silicon-on-insulator RF amplifier," Electronics Letters, Vol. 44, No. 12, pp. 1-2, 2008.

- [55] C. Chen, C. Chen, D. Yost, J. Knecht, P. Wyatt, J. Burns, K. Warner, P. Gouker, P. Healey, B. Wheeler, and C. Keast, "Wafer-scale 3D integration of silicon-on-insulator RF amplifiers," in *IEEE Proceedings of Silicon Monolithic Integrated Circuit in RF Systems*, 2009, pp. 1-4.

- [56] C. Chen, C. Chen, P. Wyatt, P. Gouker, J. Burns, J. Knecht, D. Yost, P. Healey, and C. Keast, "Effects of through-BOX vias on SOI MOSFETs," in *IEEE Proceedings of VLSI Technology, Systems and Applications*, 2008, pp. 1-2.

- [57] C. Chen, J. Burns, D. Yost, K. Warner, J. Knecht, D. Shibles, and C. Keast, "Thermal effects of three dimensional integrated circuit stacks," in *IEEE Proceedings of International SOI Conference*, 2007, pp. 91-92.

- [58] B. Aull, J. Burns, C. Chen, B. Felton, H. Hanson, C. Keast, J. Knecht, A. Loomis, M. Renzi, A. Soares, V. Suntharalingam, K. Warner, D. Wolfson, D. Yost, and D. Young, "Laser radar imager based on 3D integration of Geiger-mode avalanche photodiodes with two SOI timing circuit layers," in *IEEE Proceedings of International Solid-State Circuits Conference*, 2006, pp. 16.9-16.12.

- [59] R. Chatterjee, M. Fayolle, P. Leduc, S. Pozder, B. Jones, E. Acosta, B. Charlet, T. Enot, M. Heitzmann, M. Zussy, A. Roman, O. Louveau, S. Maitreqean, D. Louis, N. Kernevez, N. Sillon, G. Passemard, V. Pol, V. Mathew, S. Garcia, T. Sparks, and Z. Huang, "Three dimensional chip stacking using a wafer-to-wafer integration," in *IEEE Proceedings of IITC*, 2007, pp. 81-83.

- [60] P. Ledus, F. Crecy, M. Fayolle, M. Fayolle, B. Charlet, T. Enot, M. Zussy, B. Jones, J. Barbe, N. Kernevez, N. Sillon, S. Maitreqean, D. Louis, and G. Passemard, "Challenges for 3D IC integration: Bonding quality and thermal management," in *IEEE Proceedings of IITC*, 2007, pp. 210-212.

- [61] G. Poupon, N. Sillon, D. Henry, C. Gillot, A. Mathewson, L. Cioccio, B. Charlet, P. Leduc, M. Vinet, and P. Batude, "System on wafer: A new silicon concept in SIP," Proceedings of the IEEE, Vol. 97, No. 1, pp. 60-69, 2009.

- 62] www.3m.com/electronicmaterial.

- [63] S. Pargfrieder, P. Kettner, M. Privett, and J. Ting, "Temporary bonding and debonding enabling TSV formation and 3D integration for ultra-thin wafers," in *Proceedings of the 10th IEEE Electronics Packaging Tech*nology Conference, Singapore, 2008, pp. 1301-1305.