# A Drop-In High-Temperature Pb-Free Solder Paste That Outperforms High-Pb Pastes in Power Discrete Applications

Hongwen Zhang,<sup>1,\*</sup> Tyler Richmond,<sup>1</sup> Kyle Aserian,<sup>1</sup> Samuel Lytwynec,<sup>1</sup> Tybarius Harter,<sup>2</sup> and Diego Prado<sup>3</sup>

Abstract-Sn-based high-temperature Pb-free (HTLF) solder pastes have been developed as a drop-in solution to replace high-Pb solder pastes in power discrete applications. The pastes were designed with Indium Corporation's Durafuse® technology, to combine the merits of two constituent powders. A SnSb-based Ag/ Cu-containing high-temperature powder, with a melting temperature above 320°C, was designed to maintain high-temperature performance. A Sn-rich SnAgCu-Sb powder, with a melting temperature around 228°C, was added to the paste to enhance wetting and improve joint ductility. In the design, the final joint will have the low-melting phase (the melting temperature >228°C) in a controllable quantity embedded into the high-melting SnSb matrix. HTLF-1, one of the designs, maintained the bond shear strength up to 15 MPa, even around 290°C. Another design, HTLF-2, has a similar bond shear strength as Pb92.5/Sn5/Ag2.5 around 290°C, but exceeds substantially below 250°C. The power discrete components had been built with both HTLF solder pastes for both die-attach and clip-bond through the traditional high-Pb process, which demonstrated the drop-in processing compatibility. The components survived three additional surface mounting (SMT) reflows (peak temperature upto 260°C) and passed moisture sensitivity level 1 (MSL1). This confirmed that the maintained joint strength (comparable to or stronger than high-Pb), helped to keep the joint integrity within the encapsulated components in the following SMT process, even with the controlled quantity of the melting phases above 228°C. Both HTLF solder pastes outperformed Pb92.5/Sn5/Ag2.5 in the resistance from drain to source when power is on (RDS(on)), even after 1,000 cycles of temperature cycling test (TCT) under  $-55/175^{\circ}$ C, which is attributed to the intrinsic lower electrical resistivity of Sn in both HTLF pastes. Microstructural observation had shown no corner cracks for both die-attach and clip-bond joints after TCT.

Keywords—Lead-free solder, power discrete, temperature cycling, die-attach, Durafuse<sup>®</sup>

### INTRODUCTION

Development of high-temperature lead-free (HTLF) solder pastes to replace high-Pb (Pb >85 wt%) solders for dieattachment in power device applications is driven by the harmful effects of lead on human health and the environment based

The original version of this paper was presented at the 55th International Symposium on Microelectronics (IMAPS'2022), October 3-6, 2022, Boston, MA.

Indium Corporation, 34 Robinson Rd, Clinton, NY 13323

<sup>2</sup>SUNY Polytechnic Institute, 100 Seymour Road, Utica, NY 13502

<sup>3</sup>Department of Materials Science and Engineering, Cornell University, 410

Thurston Avenue, Ithaca, NY 14850

\*Corresponding author; email: hzhang@indium.com

on Restriction of Hazardous Substances (RoHS) and Waste from Electrical and Electronic Equipment (WEEE), etc. [1, 2], and the demand for improved performance of higher power efficiency [2]. The current exemption of high-lead solders is expiring in 2024. However, an extension of the exemption is possible because the drop-in solution is still in its infancy stage due to the combination of processing, performance, maturity, and cost.

The major requirements for HTLF solder pastes for power discrete applications (die-attach and clip-bond) include [2-6]: a remelting temperature higher than 260°C to maintain joint integrity while undergoing subsequent SMT reflows, a service temperature of 150°C or higher, a drop-in solution compatible with the current high-lead soldering and subsequent packaging processes, good thermal fatigue resistance, comparable or even superior electrical/thermal performance to high-lead solders, and relatively low cost. Efforts for seeking a drop-in solution with improved performance have been attempted for more than two decades. The HTLF solder candidates include: AuSn/AuSi/ AuGe [5-8], ZnAl-based [9, 10], BiAg/BiCu/BiAgX [11-15], and SnSb-based solders [3] etc. In addition to a solder alternative, transient-liquid phase soldering (TLPS), sintering, semi-sintering, and Ag-epoxy options have also been attempted for many years [16-18]. However, each of the candidates satisfied only the niche application [3, 4].

## DESIGN OF THE PASTE

Indium Corporation has been developing novel Sn-based HTLF solder pastes, which are targeted at offering a drop-in paste solution and outperforming the current high-Pb solders for industry usage. The current HTLF pastes combine the merits of both SnSb-based Ag/Cu-containing high-temperature alloys (solidus temperature at 326°C) and the commonly used Sn-rich (Sn >85 wt% and solidus temperature >217°C) SnAgCu-Sb solder alloys. The final joint will be dominated by Sn and alloyed mainly with Sb, Ag, Cu, and the doping elements. The selected combination is expected to deliver better thermal conductivity and less electrical resistivity than high-Pb since Sn is intrinsically superior to Pb in thermal and electrical performance.

SnSb-based high-temperature alloys [3] have a solidus temperature at 326°C and a liquidus temperature of around 366°C, shown in Fig. 1. The 366°C liquidus temperature is 30-40°C higher compared with high-Pb solders, which need a higher reflow temperature during soldering. SnSb-based high-temperature alloys (dominated by SnSb intermetallic compounds (IMCs)) are strong and rigid, which may risk shattering large-sized Si dies if reflowing under the high peak temperature profile [3, 4, 19-21].

The manuscript was received on February 14, 2023; revision received on May 23, 2023; accepted on May 23, 2023.

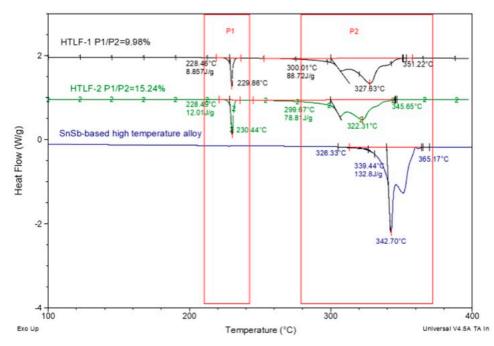

Fig. 1. DSC of HTLF-1, HTLF-2, and SnSb-based high-temperature alloys. HTLF-2 has a lower melting Sn-rich phase than HTLF-1.

Sn-rich SnAgCu-Sb solders are much more ductile and have a relatively lower-melting temperature. Combining the high-melting SnSb-based alloys and the lower-melting ductile Sn-rich alloys together is expected to lower the reflow peak temperature and make the joint more ductile in order to reduce the risk of large-sized Si die shattering.

However, the introduction of a Sn-rich alloy in the mixed solder powder paste will retain some of the Sn-rich phase in the final joint, which may render the solder to partially remelt during the subsequent SMT reflow and lead to solder squeezeout. This can cause a risk to the integrity of the die-attach and/or clip-bond joints inside the encapsulated discrete. Thus, the quantity of the low-melting Sn-rich phase must be controlled in the final joint to allow it to maintain joint integrity and resist solder squeeze-out during SMT reflow.

High-Pb solders have successfully been used for die-attach and clip-bond in power discrete for decades. Thus, in order to resist the solder squeeze-out in SMT reflow, the joint formed with the HTLF solder joints should present the similar or even higher joint strength compared with high-Pb joints during SMT reflow, which has a peak temperature up to 260°C or even higher.

After the proof of concept tests and a dozen rounds of materials screening, two pastes—HTLF-1 and HTLF-2—have been selected for sampling and testing. These have been confirmed to be able to be processed as a drop-in solution and outperform the high-Pb solders in resistance from drain to source when power is on (RDS(on)) for the tested power discrete.

#### RESULTS

#### A. Melting Behavior

Fig. 1 shows the DSC curves of these two HTLF solder pastes—HTLF-1 and HTLF-2—along with a SnSb-based high-temperature alloy. Two separate melting peaks (P1 and P2) in

the differential scanning calorimetry (DSC) curves of both HTLF-1 and HTLF-2 are associated, respectively, with the melting behavior of the low-melting Sn-rich phase and the high-melting SnSb phase, while only one high-melting peak from 326 to 365°C is seen for the SnSb-based high-temperature alloy. Compared with SnSb-based alloys, the mixed powder system dramatically changed the melting behavior, and the melting peak shifted to a lower temperature, which allows for a lower reflow peak temperature and the feasibility of a drop-in solution.

The area of each peak for both HTLF-1 and HTLF-2 indicates the heat absorption from each of the separated melting behaviors. The ratio of P1 and P2 is used to characterize the proportion of the low-melting Sn-rich phase relative to the high-melting SnSb phase in the final joint. HTLF-1 has a ratio of P1/P2 of  $\sim 10\%$  while HTLF-2 has a ratio of  $\sim 15\%$ . This indicates that the quantity of the low-melting Sn-rich phase in HTLF-2 is substantially more than that in HTLF-1.

#### B. Bond Shear Strength

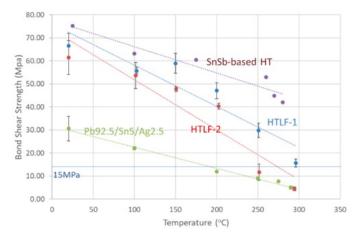

A bond shear test was conducted on the Cu/Cu joints, which were reflowed under a traditional high-temperature high-Pb profile. Pb92.5/Sn5/Ag2.5, one of the commonly used high-Pb solders, decreased the bond shear strength from 30 MPa at room temperature down to 5 MPa at 290°C. The joint shear strength of HTLF-1 always exceeded 15 MPa from room temperature up to 295°C, as shown in Fig. 2, which meets the 15 MPa-joint-strength requirement by the Die-Attach 5 (DA5) Consortium and is around three-times that of Pb92.5/Sn5/Ag2.5. The bond shear strength of HTLF-2 decreased from around 60 MPa at room temperature down to 5 MPa at 295°C, which is barely comparable to Pb92.5/Sn5/Ag2.5. As a comparison, the SnSb-based high-temperature alloy maintained a bond shear strength above 40 MPa, even around 280°C. Combining a SnSb-based high-temperature alloy with a low-melting Sn-rich alloy decreases the high-temperature

Fig. 2. Bond shear strength of HTLF pastes: HTLF-1, HTLF-2, and Pb92.5/ Sn5/Ag2.5.

strength and increases the ductility, which has been verified by the flatten peak of die shear-displacement curves. The largesized Si die shattering was not observed after both reflow and TCT [19-21], which further confirmed the effectiveness of introducing the ductile, low-melting Sn-rich phase.

Recall the existence of the low-melting Sn-rich phase in the paste, which may risk or even damage the joint integrity when soldering the power discrete onto the printed circuit board (PCB) with traditional SMT reflow. In the design, we are relying on the well-maintained high-temperature strength to reduce the risk and/or the damage of the joint. These two pastes were selected based on their high-temperature (up to 295°C) strength. HTLF-1 maintained the high-temperature (295°C) strength above 15 MPa, which is much stronger than high-Pb under the same temperature. On the other hand, HTLF-2 maintained a high-temperature (295°C) strength barely comparable to high-Pb.

## C. Voiding

The encapsulated components consisted of two  $2.5 \times 1.6 \text{ mm}^2$ Ti/Ni/Ag-Si dice bonded onto two separate pads of a Culeadframe. Clip-bond was used to interconnect the die top to Cu-lead with the same solder. During the assembling process, both HTLF-1 and HTLF-2 solder pastes, together with Pb92.5/ Sn5/Ag2.5, were used to build the package under the same high-Pb production process (reflow/cleaning/wire bond/molding). The peak temperature of the reflow was 385°C. The selection of the reflow profile was determined because of the best voiding performance among a few profile trials, which happened to be used in the production line to successfully build the high-Pb components for years in the same manufacturing facility.

Voiding levels were studied with x-ray inspection, as shown in Fig. 3. Both HTLF solder pastes (HTLF-1 and HTLF-2) and Pb92.5/Sn5/Ag2.5 have shown comparable and acceptable voiding levels. The voiding acceptance spec is 10% and below. The success of using the traditional high-Pb process for both HTLF pastes verifies the drop-in processing compatibility.

## D. Preconditioning and Moisture-Sensitive Level Tests

The moisture-sensitive level (MSL) tests on the components were conducted by following IPC/JEDEC J-STD-020D.

Fig. 3. Voiding performance of both HTLF pastes (HTLF-1 and HTLF-2) and Pb92.5/Sn5/Ag2.5 under the same high-Pb reflow profile with a peak temperature of 385°C.

Both HTLF-1 and HTLF-2 passed MSL-1. The preconditioning was done on the encapsulated components with three-times SMT reflow using the peak temperature of 260°C. After testing, ultrasonic scanning did not find any delamination inside the components. RDS(on) had a minute change before and after a three-times SMT reflow. This confirms that the sufficient high-temperature strength (≥the joint of high-Pb) does maintain the joint integrity within the encapsulated components after three-times SMT reflow. However, the partial remelting may still grow the interfacial IMCs slightly, and it may be associated with the minute change of RDS(on). RDS(on) of both HTLF pastes was superior to that of Pb92.5/Sn5/Ag2.5, which will be shown later.

## E. Temperature Cycling Test

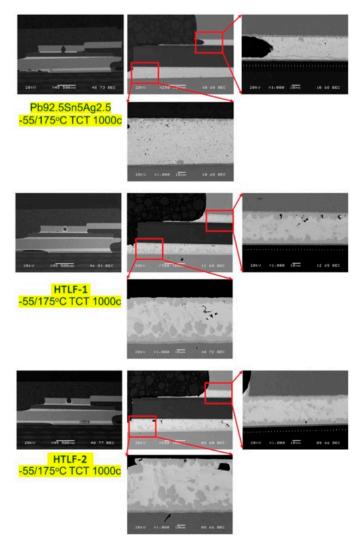

After conducting the MSL tests, temperature cycling tests  $(-55/175^{\circ}C)$  were also done on the encapsulated components following the AEC Q101 procedure. After 1,000 cycles of TCT, the components were taken out of the chamber, cross-sectioned, and prepared for microstructural observation. Both Pb92.5/Sn5/Ag2.5 and the two HTLF solder pastes had shown neither corner cracks nor delamination after 1,000 cycles of TCT for both dieattach (die to leadframe) and clip-bonded (clip to die top) joints, as shown in Fig. 4.

Both HTLF-1 and HTLF-2 are Sn-rich solders, while Pb92.5/ Sn5/Ag2.5 have limited Sn (5 wt%). As known, Sn dominates the interfacial IMC formation. Compared with high-Pb solder, HTLF-1 and HTLF-2 have shown thicker interfacial IMCs, which is expected because of the high-Sn content.

## F. Resistance from Drain to Source When Power Is on

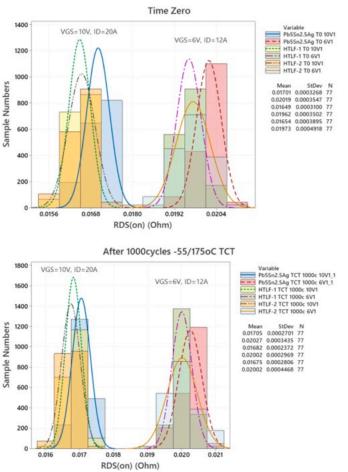

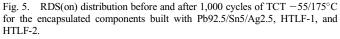

RDS(on) is the resistance from drain to source when power is on. RDS(on) of the components had been measured before and after TCT (-55/175°C). Fig. 5 shows the RDS(on) distribution before and after 1,000 cycles of TCT. Both HTLF-1 and HTLF-2 have similar RDS(on) values and are smaller than Pb92.5/Sn5/Ag2.5 before and after TCT, which indicates that both HTLF pastes outperform Pb92.5/Sn5/Ag2.5 in electrical performance. HTLF-1 has a distribution shape similar to Pb92.5/ Sn5/Ag2.5, while HTLF-2 has a wider distribution range. So far, we did not know exactly the reason for the different RDS(on) distribution, and the current high-Pb process has been assumed to contribute to the difference. In this case, it seems HTLF-1 is more compatible to the current high-Pb process to achieve a narrower distribution. It was also noticed that the difference in

Fig. 4. Joint morphology of the encapsulated components after 1,000 cycles of TCT ( $-55/175^{\circ}$ C) from Pb92.5/Sn5/Ag2.5, HTLF-1, and HTLF-2.

RDS(on) between HTLF pastes and Pb92.5/Sn5/Ag2.5 became less after 1,000 cycles of TCT, as shown in Fig. 5.

In order to clarify the trend of RDS(on) change with TCT, Fig. 6 summarizes the change of RDS(on) with TCT cycle numbers at the 200 cycles interval for both HTLF pastes and Pb92.5/Sn5/Ag2.5. First, both HTLF-1 and HTLF-2 clearly outperformed Pb92.5/Sn5/Ag2.5 in RDS(on) in the entire TCT. The results validate the design that the intrinsic lower electrical resistivity of Sn-based alloys than Pb improves performance. Second, HTLF-1 was shown to be slightly better than HTLF-2. The process optimization may help reduce the difference between these two HTLF pastes. Third, the difference in RDS(on) between the HTLF pastes and Pb92.5/Sn5/ Ag2.5 becomes smaller after 1,000 cycles of TCT. After TCT, both HTLF pastes and Pb92.5/Sn5/Ag2.5 have no corner cracks or delamination from joint morphology as shown in Fig. 4. Therefore, the RDS(on) shift is possibly attributed to the solder joint microstructural evolution and the interfacial IMC growth.

#### DISCUSSION

The existence of the low melting phase (melting point  $\sim$ 228°C) with the controlled quantity in HTLF-1 and HTLF-2 can still allow the encapsulated components surviving MSL1

Fig. 6. RDS(on) of the encapsulated components for Pb92.5/Sn5/Ag2.5, HTLF-1, and HTLF-2.

and 1,000 cycles of TCT  $-55/175^{\circ}$ C. The intrinsic superior electrical and thermal properties of Sn-based alloys indeed presented the improved RDS(on) compared with high-Pb solder. All these data have confirmed the success of the design of combining the merits of high-temperature SnSb-based solder powder and Sn-rich solder powders in one paste to deliver a feasible lead-free solution to replace high-Pb for die-attach and clip-bond application in power discrete components.

Additional attempts with HTLF-1 paste have been extended to bigger size of Si die up to  $6.8 \times 4.7 \text{ mm}^3$  for die-attach and clip-bond power discrete (TO-Leadless), which had passed all the evaluation and the results will be reported later [22].

HTLF-1 has also demonstrated the capability for the modulelevel die-attach application, with Si die sizes ranging from  $6.8 \times 6.8 \text{ mm}^2$  up to  $12.1 \times 8.7 \text{ mm}^2$ , after tested under TCT (-50/ 175°C, 30 min dwelling), thermal aging at 200°C, and power cycling (30/150°C, Ic = 145 A and ton/toff = 0.5 s/3.1 s) [23].

Although the feasibility of success has been verified from more and more testing sites, the challenges are seen as well. The compatibility of the current die metallization design with lead-free solder must be considered first. To make Si dies solderable, multiple layers of metallization on the Si die surface must be plated. Ti/Ni/Ag was one of the commonly used metallization combinations. For high-Pb solder, Sn is the element used to wet and react, while Pb will not react with Cu, Ni, and Ag to form IMCs. The interfacial IMC formation during soldering occurs between Sn from high-Pb solder and the combination of both Ni and Ag layers. Due to the limited Sn content in high-Pb solder, the thickness of the solderable Ni and the protection Ag layers could be as thin as 200 nm of each. Pb is also soft enough to absorb most of the strain from die-attach and clip-bond joints. Thus, the interfacial bonding failure at the Si dies surface is hardly seen. Both HTLF-1 and HTLF-2 solders had more than 50% Sn, which will continuously react with Ni and Ag metallization from Si die during soldering. If those layers are too thin, they will be fully consumed to form interfacial IMCs and detached from the bottom Ti layer, which was used as the adhesion layer between the Si and Ni bonding interfaces. Due to the poor wettability of the Ti layer, lead-free solders may de-wet from the Ti surface. This will cause poor voiding due to the interfacial dewetting and thus weaken the bonding interface. The thicker metallization layer on the Si die surface, especially the thicker solderable Ni layer, is recommended if moving toward lead-free. In practice, 500 nm Ni metallization and 200 nm Ag metallization on Si die surface has proven high compatibility as a drop-in solution to replace high-Pb solders. The metallization of 350 nm Ni and 200 nm Ag on Si dies can also survive if using cold and/or short reflow profiles. The authors are actively working with the DA5 consortium and some partners to study the impacts thoroughly when using HTLF solders to replace high-Pb ones in power semiconductor packaging.

#### CONCLUSIONS

Two Sn-based HTLF solder pastes combining the merits of two constituent powders were prepared and tested as drop-in solutions to replace high-Pb solder pastes in power discrete applications. Both HTLF solder pastes (HTLF-1 and HTLF-2) can be successfully processed to build encapsulated components using the current high-Pb production process. Voiding and MSL performance are similar for both HTLF solder pastes and comparable to Pb92.5/Sn5/Ag2.5. Neither cracks nor delamination were observed in the joint cross-section morphology after 1,000 cycles of TCT ( $-55/175^{\circ}$ C). Both HTLF solder pastes substantially outperformed Pb92.5/Sn5/Ag2.5 in RDS(on) before and after TCT. The current results validated the new design; the two pastes developed on the basis of the design (HTLF-1 and HTLT-2) have been successfully demonstrated in production with the current high-Pb process, although optimization may still be needed. The performance of the components with HTLF pastes is superior to that of Pb92.5/Sn5/Ag2.5 as was desired in the design.

In conclusion, HTLF-1 and HTLF-2 provided new drop-in options for replacing high-Pb in power discrete applications, with superior performance compared with high-Pb.

### ACKNOWLEDGMENTS

The authors would like to acknowledge their co-workers for their help and support, namely Leo Hu, David Hu, Christine LaBarbera, Lee Kresge, Yan Liu, Dean Payne, and Sze Pei Lim, etc. The authors would also like to thank their industry partners for their support in testing and for their valuable discussion and comments.

# References

- S. Menon, E. George, M. Osterman, and M. Pecht, "High lead solder (over 85%) solder in electronic industry: ROHS exemptions and alternatives," *Journal of Materials Science Materials in Electronics*, Vol. 26, pp. 4021-4030, 2015.

- [2] S.P. Lim, B. Pan, H. Zhang, W. Ng, B. Wu, K.S. Siow, S. Sabne, and M. Tsuriya, "High-temperature Pb-free die attach material project phase I: survey result," ICEP 2017 Proceedings, Yamagata, Japan, TA4-4, April 19-22, 2017.

- [3] H. Zhang and N.C. Lee, "Chapter 6: High-temperature lead-free bonding materials—the need, the potential candidates, and the challenges," *Lead-Free Soldering Process Development and Reliability*, J. Bath, Ed., Wiley, Hoboken, NJ, USA, pp. 155-190, 2020.

- [4] H. Zhang, J. Minter, and N.C. Lee, "A brief review on high-temperature, Pb-free die attach materials," *Journal of Electronic Materials*, Vol. 48, No. 1, pp. 201-210, 2019.

- [5] J.W. Ronnie Teo, F.L. Ng, L.S. Kip Goi, Y.F. Sun, Z.F. Wang, X.Q. Shi, J. Wei, and G.Y. Li, "Microstructure of eutectic 80Au/20Sn solder joint in laser diode package," *Microelectronic Engineering*, Vol. 85, pp. 512-517, 2008.

- [6] S. Tanimoto, K. Matsui, Y. Murakami, H. Yamaguchi, and H. Okumura, "Assessment of Au-Ge die attachment for an extended junction temperature range in power applications," Proceeding of 2010 International Conference and Exhibition of High-Temperature Electronics, TA1, Albuquerque NM, USA, May 11-13, 2010.

- [7] S. Tanimoto, K. Matsui, Y. Zushi, S. Sato, Y. Murakami, M. Takamori, and T. Iseki, "Common metal die-attach for SiC power devices operated in an extended junction temperature range," *Materials Science Forum*, Vols. 717-720, p. 853, 2012.

- [8] G. Zeng, S. McDonald, and K. Nogita, "Development of high-temperature solders: review," *Microelectronics and Reliability*, Vol. 52, pp. 1306-1322, 2012.

- [9] A. Haque, B.H. Lim, A.S.N.A. Haseeb, and H.H. Masjuki, "Die-attach properties of Zn-Al-Mg-Ga based high-temperature lead-free solder on Cu lead-frame," *Journal of Materials Science Materials in Electronics*, Vol. 23, pp. 115-123, 2012.

- [10] M. Rettenmayr, P. Lambracht, B. Kempf, and C. Tschudin, "Zn-Al based alloys as Pb-free solders for die attach," *Journal of Electronic Materials*, Vol. 31, pp. 278-285, 2002.

- [11] H. Zhang and N.C. Lee, "Mixed Solder Alloy Paste", US Patent No. 9017446 B2, 2015.

- [12] H. Zhang and N.C. Lee, "Mixed Solder Alloy Paste", US Patent No. 9636784 B2, 2017.

- [13] H. Zhang and N.C. Lee, "Reliability of BiAgX solder as a drop-in solution for high-temperature lead-free die-attach applications," *SMTA Journal*, Vol. 26, pp. 28-32, 2013.

- [14] H. Zhang and N.C. Lee, "High-reliability, high-melting, lead-free, mixed solder paste system—BiAgX," *The Review of Scientific Instruments*, Vol. 92, p. 099501, 2021.

- [15] Z. Shen, R.W. Johnson, and M.C. Hamilton, "SiC power device die attach for extreme environments," *IEEE Transactions on Electron Devices*, Vol. 62, No. 2, pp. 346-353, 2015.

- [16] R. Dudek, P. Sommer, A. Fix, S. Rzepka, and B. Michel, "Reliability issues for high-temperature interconnections based on transient liquid phase soldering", Proceeding of 14th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, pp. 1-8, Wroclaw, Poland, April 14-17, 2013.

- [17] K.S. Siow, "Are sintered silver joints ready for use as interconnect material in microelectronic packaging," *Journal of Electronic Materials*, Vol. 43, pp. 947-961, 2014.

- [18] V.R. Manikam and K. Cheong, "Die-attach materials for high-temperature applications: a review," *IEEE Transactions on Components, Packaging,* and Manufacturing Technology, Vol. 1, No. 4, pp. 457-478, 2011.

- [19] H. Zhang, S. Lytwynec, H. Wang, J. Geng, F. Mutuku, and N.C. Lee, US Patent Publication No. 0339344A1, "Lead-free solder paste with mixed powders for high temperature applications", 2021.

[20] H. Zhang, "Durafuse<sup>®</sup> HT: A drop-in high-temperature Pb-free (HTLF)

- [20] H. Zhang, "Durafuse" HT: A drop-in high-temperature Pb-free (HTLF) solution that outperforms high-Pb solders," APEC Proceedings, S10.2, Houston, TX, 20-24 March 2022.

- [21] H. Zhang, S.P. Lim, S. Lytwynec, T. Richmond, and T. Harter, "A drop-in high-temperature lead-free solder paste that outperforms high-Pb pastes in power discrete applications," ICEP Proceedings, pp. 69-70, Hokkaido, Japan, 11-14 May 2022.

- [22] H. Zhang, Y.J. Hu, D. Hu, B. Chen, et al. "A TO-leadless power MOSFET built with high-temperature Pb-free solder," to be submitted.

- [23] M. Morshed, Y. Wang, L.R. Billa, T. Grant, M. Mat, and D. Payne, "Hightemperature lead-free solder alloy for high power semiconductor device packaging applications," Proceedings of PCIM Europe, pp. 1389-1393, Nuremberg, Germany, 9-11 May 2023.